## EE 435

Lecture 25

**Data Converter Architectures**

. · · · · Review from last lecture . · · · ·

## **Data Converters**

### **Types:**

A/D (Analog to Digital)

Converts Analog Input to a Digital Output

D/A (Digital to Analog)

Converts a Digital Input to an Analog Output

A/D is the world's most widely used mixed-signal component

D/A is often included in a FB path of an A/D

A/D and D/A fields will remain hot indefinitely technology advances make data converter design more challenging embedded applications designs often very application dependent

### • • • • Review from last lecture .• • • •

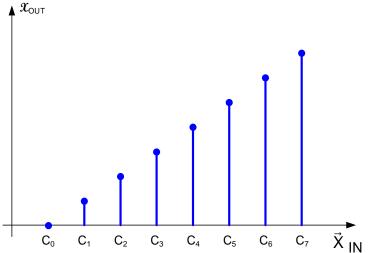

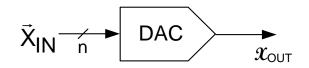

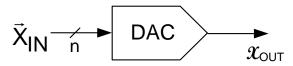

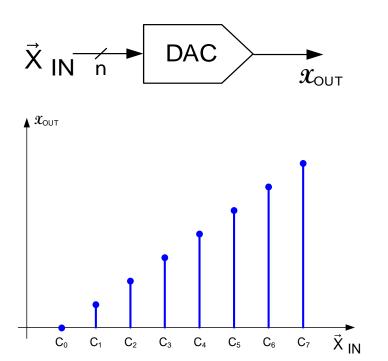

# D/A Converters $\vec{x}_{IN}$

$$\vec{X}$$

IN n DAC  $x_{OUT}$

For this ideal DAC

$$\mathcal{X}_{OUT} = X_{REF} \left( \frac{b_{n-1}}{2} + \frac{b_{n-2}}{4} + \frac{b_{n-3}}{8} + \dots + \frac{b_1}{2^{n-1}} + \frac{b_0}{2^n} \right)$$

$$\mathcal{X}_{OUT} = X_{REF} \sum_{j=1}^{n} \frac{b_{n-j}}{2^j}$$

- Number of outputs gets very large for n large

- Spacing between outputs is X<sub>REF</sub>/2<sup>n</sup> and gets very small for n large

. • • • • Review from last lecture . • • •

# Applications of DACs

- Waveform Generation

- Voltage Generation

- Analog Trim or Calibration

- Industrial Control Systems

- Feedback Element in ADCs

- •

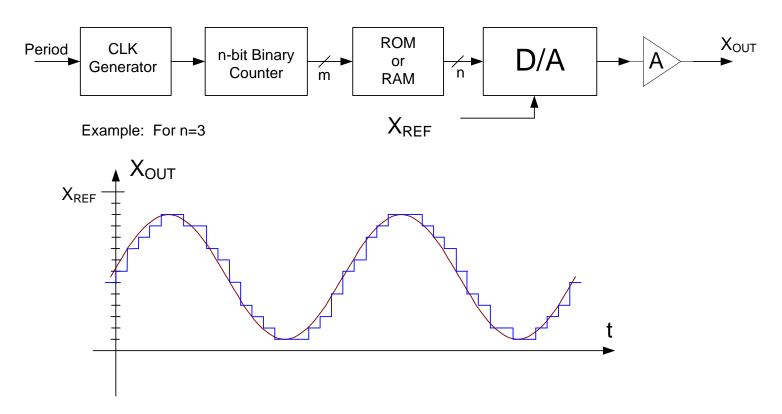

## Waveform Generation with DACs

### Sine Wave Generator

Distortion of the desired waveforms occurs due to both time and amplitude quantization

Often a filter precedes or follows the buffer amplifier to smooth the output waveform

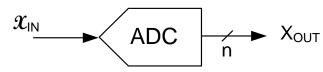

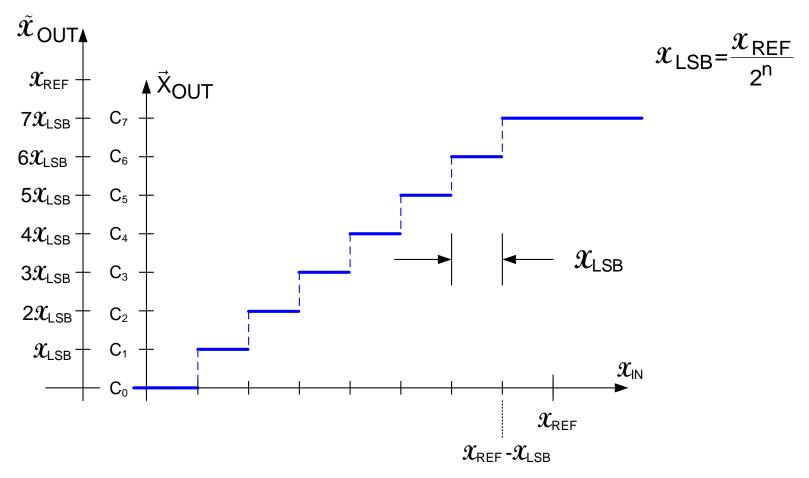

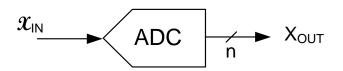

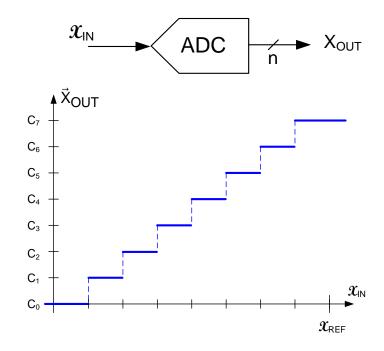

## A/D Converters

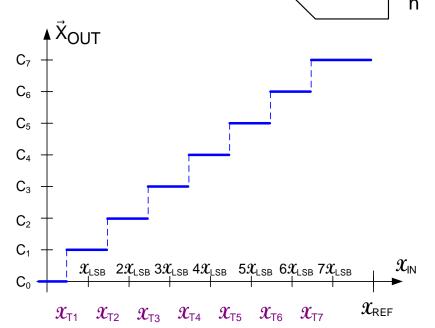

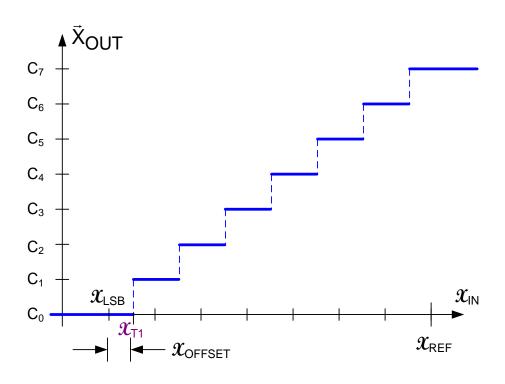

An Ideal ADC transfer characteristic (3-bits)

$$\vec{X}_{OUT} = < d_{n-1}, d_{n-2}, ...d_0 >$$

The second vertical axis, labeled  $\mathcal{ ilde{X}}_{OUT}$  ,is the interpreted value of  $\vec{x}_{OUT}$

Review from last lecture. D Converters

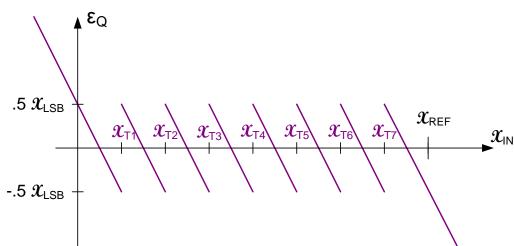

**Quantization Errors**

**Another Ideal ADC**

$$\mathcal{X}_{T1} = \mathcal{X}_{LSB}/2$$

$\mathcal{X}_{\mathsf{IN}}$

**ADC**

$$\varepsilon_Q = \tilde{\mathcal{X}}_{\mathsf{OUT}} - \mathcal{X}_{\mathsf{IN}}$$

Magnitude of  $\epsilon_Q$  bounded by ½  $\mathcal{X}_{LSB}$

Is the performance of this ideal ADC really better than that of the previous ideal ADC?

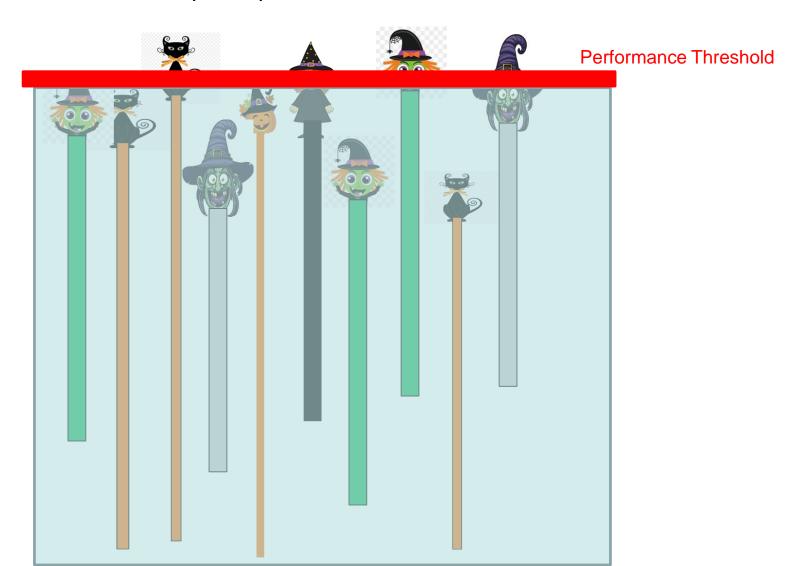

### **Data Converter Design Approach**

Ultimately lowering (enhancing) performance threshold makes it difficult to further improve performance

#### • • • • Review from last lecture .• • • •

## Data Converter Architectures

### **Nyquist Rate**

Flash

Charge Redistribution

Pipeline

Two-step and Multi-Step

Interpolating

Algorithmic/Cyclic

Successive Approximation (Register) SAR

Single Slope / Dual Slope

Subranging

Folded

Interleaved

**Current Steering**

R-string

Charge Redistribution

Algorithmic

R-2R (ladder)

**Pipelined**

Subranging

### **Over-Sampled (Delta-Sigma)**

Discrete-time

First-order/Higher Order

Continuous-time

Discrete-time

First-order/Higher Order

Continuous-time

. • • • • Review from last lecture . • • • •

## Data Converter Architectures

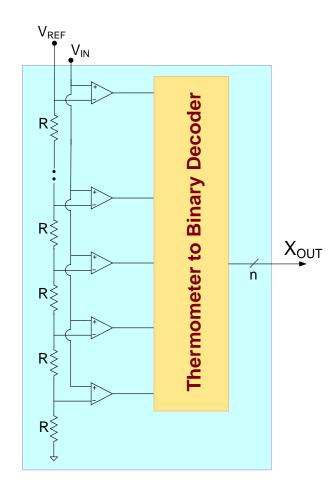

### **Flash**

. • • • • Review from last lecture . • • • •

## Data Converter Architectures

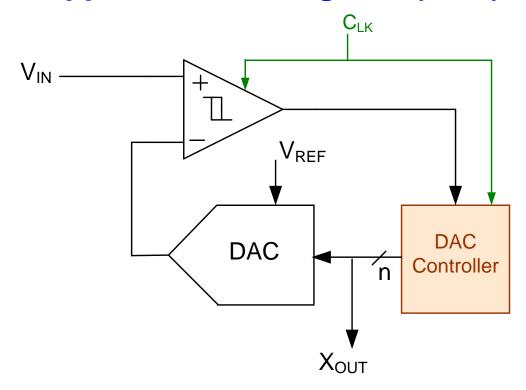

### **Successive Approximation Register (SAR)**

#### . • • • • Review from last lecture . • • • •

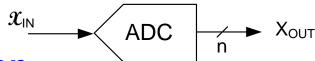

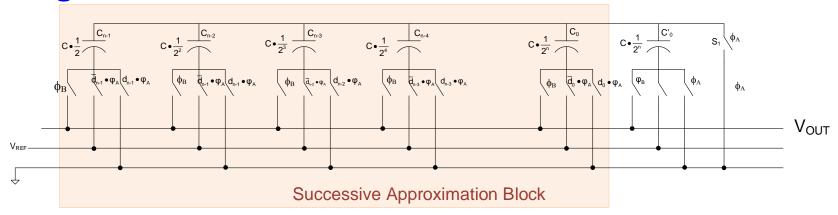

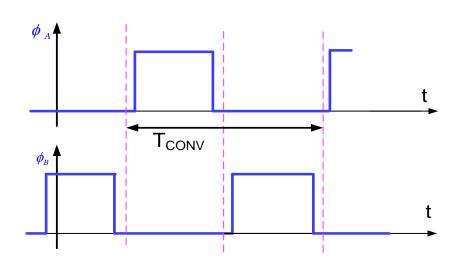

## Data Converter Architectures

**Charge Redistribution**

Redistribute charge with switches to drive Vx to 0

$$Q_{SAM} = V_{IN} \left( \sum_{i=0}^{n-1} C_i + \left[ C_0 \right] \right) = V_{IN} \left( \sum_{i=0}^{n-1} \frac{C}{2^{n-i}} + \left[ \frac{C}{2^n} \right] \right) = V_{IN} C$$

$$Q_{REDIS} = V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}}$$

$$Q_{SAM} = Q_{REDIS}$$

$$V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}} = V_{IN} C$$

$$V_{IN} = V_{REF} \sum_{i=0}^{n-1} \frac{d_i}{2^{n-i}}$$

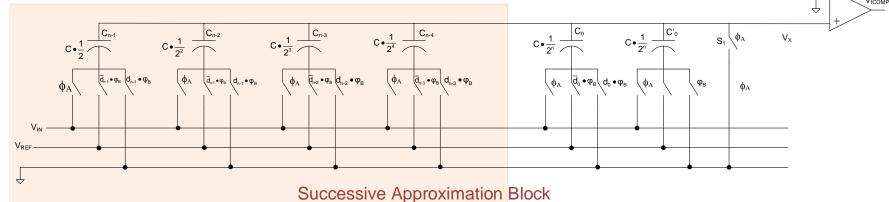

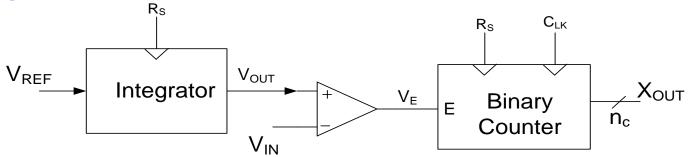

**Single Slope**

Comparator Changes States when

$$V_{IN} = I_0 \int_0^{t_{TR}} V_{REF} dT = I_0 t_{TR} V_{REF}$$

Counter stops when

$$V_{IN} = t_{TR} V_{REF} I_0 \cong n_{COUNT} T_{CLK} V_{REF} I_0 \longrightarrow n_{COUNT} \cong \frac{V_{IN}}{V_{REF}} \bullet \left(\frac{f_{CLK}}{I_0}\right)$$

$$\text{If calibrate so that} \quad 2^n \cong \left(\frac{f_{\text{CLK}}}{I_0}\right) \quad n_{\text{COUNT}} \cong \frac{V_{\text{IN}}}{V_{\text{REF}}} \bullet 2^n \quad \Longleftrightarrow \quad V_{\text{IN}} \cong \frac{n_{\text{COUNT}}}{2^n} \bullet V_{\text{REF}}$$

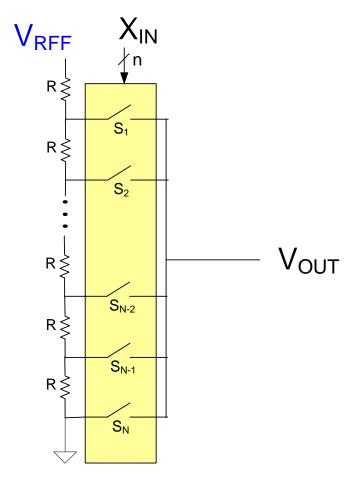

**R-String**

X<sub>IN</sub> is decoded to close one switch

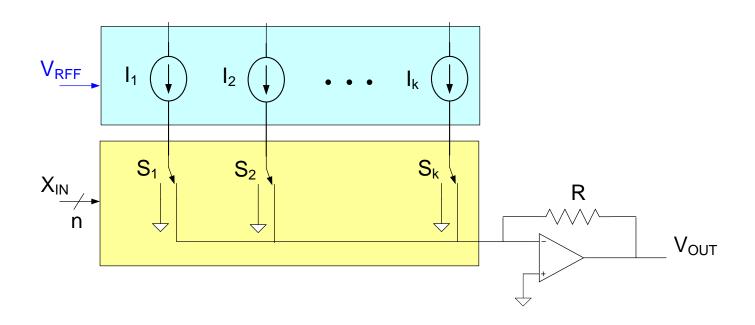

### **Current Steering**

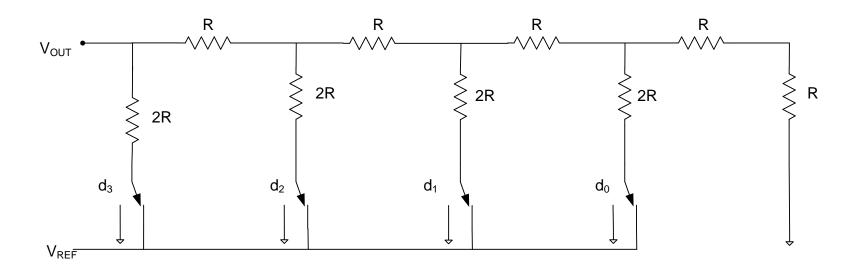

**R-2R** (4-bits)

By superposition:

$$V_{\text{OUT}} = V_{\text{REF}} d_3 \bullet \frac{1}{2} + V_{\text{REF}} d_2 \bullet \frac{1}{4} + V_{\text{REF}} d_1 \bullet \frac{1}{8} + V_{\text{REF}} d_0 \bullet \frac{1}{16} = V_{\text{REF}} \sum_{k=0}^{3} \frac{d_k}{2^{4-k}} = V_{\text{REF}} \sum_{k=1}^{4} \frac{d_{4-k}}{2^k} = V_{\text{REF}} \sum_{k=1}^{4} \frac{d_{4-k}}{2^$$

### **Charge Redistribution**

$$Q_{SET} = V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}}$$

$$Q_{RDIS} = V_{OUT} \left( \sum_{i=0}^{n-1} C_i + \left[ C_0 \right] \right) = V_{OUT} \left( \sum_{i=0}^{n-1} \frac{C}{2^{n-i}} + \left[ \frac{C}{2^n} \right] \right) = V_{OUT} C$$

$$Q_{SFT} = Q_{RDIS}$$

$$V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}} = V_{OUT}C$$

$$V_{OUT} = V_{REF} \sum_{i=0}^{n-1} \frac{d_i}{2^{n-i}}$$

- Many more data converter architectures have been proposed

- Many are some variant of those listed above

- Recall: All typically are perfect if components are ideal

- The major nonideal effects are usually due to one of four issues:

- Matching performance is not acceptable

- Speed is limited by parasitics

- Nonlinearities degrade performance

- Noise is excessive

- Most data converter design involves sequentially identifying dominant nonideal effect and developing ways to lower it

- Important to observe methods for mitigating nonideal effects as they are often used repeatedly

### Performance Characterization of Data Converters

- A very large number of parameters (2<sup>n</sup>) characterize the static performance of an ADC!

- And even more parameters needed to characterize the dynamic performance of an ADC

- A large (but much smaller) number of parameters are invariably used to characterize a data converter

- Performance parameters of interest depend strongly on the application

- Very small number of parameters of interest in many/most applications

- "Catalog" data converters are generally intended to satisfy a wide range of applications and thus have much more stringent requirements placed on their performance

- Custom application-specific data converter will generally perform much better than a "catalog" part in the same application

## A/D Converters

### What types are really used?

Consider catalog parts from one vendor – Analog Devices (Jan 2017)

Flash 2 SAR 233 Pipelined 242 Sigma-Delta 81

Total 559

### What do ADCs cost?

### A/D Converters

| Part #   | Hardware     | ADC \$\frac{1}{4}\$ Resolution (bits) | ADC Output Sample Rate | ADC • H   | Architecture | US Price 1000 to 4999 (\$ US) | INL in LSB (typ) | ) FE    | Vin  Range (typ) (V p-p) | ADC SNR  in dBFS (typ) (dBFS) | Power Dissipation (typ) (W) |

|----------|--------------|---------------------------------------|------------------------|-----------|--------------|-------------------------------|------------------|---------|--------------------------|-------------------------------|-----------------------------|

|          | 0 Values ▼   | 16 Values ▼                           | 16.6 - 2.5G            | 13 Value▼ | 7 Values S ▼ | 0.95 - 91                     | 6.5 0.1          | - 33.55 | 0.078 - 40               | 47 - 107.8                    | 21u - 4.2                   |

| AD7492-5 | <b>=</b> (   | 12                                    | 1.25M                  | -         | SAR          | $\overline{}$                 | **               | -       | -                        | -                             | 16.5r                       |

| AD7170   | <b>Z</b>     | 12                                    | 125                    | 1         | Sigma-Delta  | \$0                           | .95              | -       | -                        | -                             | 150                         |

| AD7478   | -            | 8                                     | 1M                     | 1         | SAR          | \$0                           | .96              | -       | 5.25                     | -                             | 17.5m                       |

| AD7478A  | -            | 8                                     | 1.2M                   | 1         | SAR          | \$1                           | .12              | -       | 5.25                     | -                             | 17.5n                       |

| AD7171   | <b>% =</b> ( | 16                                    | 125                    | 1         | Sigma-Delta  | \$1                           | .15              | -       | -                        | -                             | 150                         |

| AD7999   | -            | 8                                     | 140k                   | 4         | SAR          | \$1                           | .35              | -       | 5.5                      | -                             | 4.7m                        |

| AD7468   | <b>=(</b> )  | 8                                     | 320k                   | 1         | SAR          | \$1                           | .35              | -       | 3.6                      | -                             | 570 <sub>k</sub>            |

| AD7091   | <b>=(</b>    | 12                                    | 1M                     | 1         | SAR          | \$1                           | .60              | -       | 5.25                     | -                             | 2.4n                        |

| AD7904   | <b>=(</b> )  | 8                                     | 1M                     | 4         | SAR          | \$1                           | .68              | -       | 5.1                      | -                             | 13.5n                       |

| AD7910   | <b>=(</b>    | 10                                    | 250k                   | 1         | SAR          | \$1                           | .77              | -       | 5.25                     | -                             | 15n                         |

| AD7995   | <b>% =</b> ( | 10                                    | 140k                   | 4         | SAR          | \$1                           | .80              | -       | 5.5                      | -                             | 4.4n                        |

| AD7276   | <b>=(</b>    | 12                                    | 3M                     | 1         | SAR          | \$1                           | .85              | -       | 3.6                      | -                             | 19.8n                       |

| AD7908   | -            | 8                                     | 1M                     | 8         | SAR          | \$1                           | .87              | -       | 5.05                     | -                             | 13.5n                       |

### What do ADCs cost?

### A/D Converters

|   | D-14        |              | 1000                   |                        | 100       |                     | Ho Diag                                  | . Du                             |                                    | ADO OND . "                   |                                         |

|---|-------------|--------------|------------------------|------------------------|-----------|---------------------|------------------------------------------|----------------------------------|------------------------------------|-------------------------------|-----------------------------------------|

| ı | Part #      | Hardware     | ADC CRESOlution (bits) | ADC Output Sample Rate | ADC • H   | Device Architecture | US Price<br>1000 to 1<br>4999<br>(\$ US) | INL in<br>LSB<br>(typ)<br>(LSBs) | Vin ‡<br>Range<br>(typ)<br>(V p-p) | ADC SNR  in dBFS (typ) (dBFS) | Power \$\displays Dissipation (typ) (W) |

| ₽ |             | 0 Values▼    | 16 Values ▼            | 16.6 - 2.5G            | 13 Value▼ | 7 Values S ▼        | 0.95 - 916.5                             | 0.1 - 33.5                       | 0.078 - 40                         | 47 - 107.8                    | 21u - 4.2                               |

|   | AD10465     | <b>!!</b> () | 14                     | 65M                    | 2         | Pipelined           | \$916.53                                 |                                  | - 4                                | -                             | 3.5                                     |

|   | ad9625-2600 | <b>={</b> }  | 12                     | -                      | 1         | Pipelined           | \$837.42                                 | 1                                | 1.1                                | 58.1                          | 4                                       |

|   | ad9625-2500 | <b>=</b> ()  | 12                     | 2.5G                   | 1         | Pipelined           | \$735.00                                 | 1                                | 1.1                                | 58.3                          | 3.9                                     |

|   | AD9691      | -            | 14                     | 1250M                  | 2         | Pipelined           | \$692.75                                 | 2.6                              | 1.58                               | 63.4                          | 3.8                                     |

|   | AD9680-1250 | <b>=</b>     | 14                     | 1.25G                  | 2         | Pipelined           | \$692.75                                 | 3                                | 1.58                               | 63.6                          | 3.7                                     |

|   | ad9625-2000 | <b>=</b> 3   | 12                     | 2G                     | 1         | Pipelined           | \$624.75                                 | 0.9                              | 1.1                                | 59.5                          | 3.48                                    |

|   | AD9680-1000 | <b>=</b> 3   | 14                     | 1G                     | 2         | Pipelined           | \$584.38                                 | 2.5                              | 1.7                                | 67.2                          | 3.3                                     |

|   | AD9694      | <b>::</b> () | 14                     | 500M                   | 4         | Pipelined           | \$488.75                                 | 1                                | -                                  | 67.1                          | 1.66                                    |

### Resolution?

3 bits to 24 bits (one at 32 bits)

## Real Simple Concepts

$$x_{OUT} = X_{REF} \sum_{j=1}^{n} \frac{b_{n-j}}{2^{j}}$$

$$\mathcal{X}_{REF} \sum_{j=1}^{n} \frac{\alpha_{n-j}}{2^{j}} = \mathcal{X}_{IN} + \epsilon$$

- Characterizing performance is a tedious task

- Users must be aware of the "quirks" inherent in data converters

- Designers must understand performance requirements

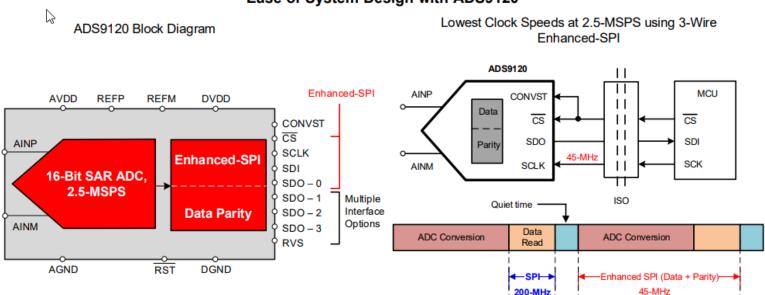

ADS9120

SBAS710A - SEPTEMBER 2016-REVISED JUNE 2017

### ADS9120 16-Bit, 2.5-MSPS, 15.5-mW, SAR ADC With Enhanced Performance Features

| QTY | UNIT PRICE |

|-----|------------|

| 1   | \$20.48000 |

| 10  | \$18.82100 |

| 25  | \$18.04120 |

| 100 | \$15.11560 |

#### 1 Features

- · Sample Rate: 2.5 MSPS

- No Latency Output

- · Excellent DC and AC Performance:

- INL: ±0.25 LSB

- DNL: ±0.6 LSB

- SNR: 96 dB, THD: –118 dB

- · Wide Input Range:

- Unipolar Differential Input Range: ±V<sub>REF</sub>

- V<sub>REF</sub> Input Range: 2.5 V to 5 V, Independent of AVDD

- Low-Power Dissipation:

- 9 mW at 2.5 MSPS (AVDD Only)

- 15.5 mW at 2.5 MSPS (Total)

- Flexible Low-Power Modes Enable Power Scaling with Throughput

- Enhanced-SPI (multiSPI™) Digital Interface

- JESD8-7A-Compliant Digital I/O at 1.8-V DVDD

- Fully-Specified Over Extended Temperature Range: -40°C to +125°C

- Small Footprint: 4-mm × 4-mm VQFN

#### Ease of System Design with ADS9120

### **\_** 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                        | MIN | NOM | MAX | UNIT |

|------|------------------------|-----|-----|-----|------|

| AVDD | Analog supply voltage  |     | 1.8 |     | V    |

| DVDD | Digital supply voltage |     | 1.8 |     | V    |

| REFP | Positive reference     |     | 5   |     | V    |

#### **T 6.5** Electrical Characteristics

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2.5 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C, unless otherwise noted. All typical values are at  $T_A$  = 25°C.

|                      | PARAMETER                                              | TEST CONDITIONS                                                                               | MIN                          | TYP                   | MAX                          | UNIT               |

|----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------|-----------------------|------------------------------|--------------------|

| ANALOG               | SINPUT                                                 |                                                                                               |                              |                       |                              |                    |

| FSR                  | Full-scale input range<br>(AINP – AINM) <sup>(1)</sup> |                                                                                               | -V <sub>REF</sub>            |                       | $V_{REF}$                    | V                  |

| V <sub>IN</sub>      | Absolute input voltage (AINP and AINM to REFGND)       |                                                                                               | -0.1                         |                       | V <sub>REF</sub> + 0.1       | ٧                  |

| V <sub>CM</sub>      | Common-mode voltage range (AINP + AINM) / 2            |                                                                                               | (V <sub>REF</sub> / 2) – 0.1 | V <sub>REF</sub> / 2  | (V <sub>REF</sub> / 2) + 0.1 | V                  |

| <u> </u>             | Innut conscitones                                      | In sample mode                                                                                |                              | 60                    |                              | , F                |

| C <sub>IN</sub>      | Input capacitance                                      | In hold mode                                                                                  |                              | 4                     |                              | pF                 |

| I <sub>IL</sub>      | Input leakage current                                  |                                                                                               |                              | ±1                    |                              | μΑ                 |

| VOLTAG               | E REFERENCE INPUT                                      |                                                                                               |                              |                       |                              |                    |

| V <sub>REF</sub>     | Reference input voltage range                          |                                                                                               | 2.5                          |                       | 5                            | V                  |

| I <sub>REF</sub>     | Reference input current                                | Average current, V <sub>REF</sub> = 5 V,<br>2-kHz, full-scale input,<br>throughput = 2.5 MSPS |                              | 1.3                   |                              | mA                 |

| DC ACC               | URACY                                                  |                                                                                               |                              |                       |                              |                    |

|                      | Resolution                                             |                                                                                               |                              | 16                    |                              | Bits               |

| NMC                  | No missing codes                                       |                                                                                               | 16                           |                       |                              | Bits               |

| INII                 | Internal months control                                | T <sub>A</sub> = -40°C to +85°C                                                               | -0.6                         | ±0.25 <sup>(2)</sup>  | 0.6                          | LSB <sup>(3)</sup> |

| INL                  | Integral nonlinearity                                  | T <sub>A</sub> = -40°C to +125°C                                                              | -0.7                         | ±0.25 <sup>(2)</sup>  | 0.7                          | LSB                |

| DNL                  | Differential penlineerity                              | T <sub>A</sub> = -40°C to +85°C                                                               | -0.6                         | ±0.25 <sup>(2)</sup>  | 0.6                          | LSB                |

| DNL                  | Differential nonlinearity                              | T <sub>A</sub> = -40°C to +125°C                                                              | -0.7                         | ±0.25                 | 0.7                          | LSB                |

| E <sub>(IO)</sub>    | Input offset error                                     |                                                                                               | -1                           | ±0.025 <sup>(2)</sup> | 1                            | mV                 |

| dV <sub>OS</sub> /dT | Input offset thermal drift                             |                                                                                               |                              | 1                     |                              | μV/°C              |

| GE                   | Gain error                                             |                                                                                               | -0.02                        | ±0.01 <sup>(2)</sup>  | 0.02                         | %FS                |

| G <sub>E</sub> /dT   | Gain error thermal drift                               |                                                                                               |                              | 0.25                  |                              | ppm/°C             |

|                      | Transition noise                                       |                                                                                               |                              | 0.35                  |                              | LSB                |

| CMRR                 | Common-mode rejection ratio                            | At dc to 20 kHz                                                                               |                              | 80                    |                              | dB                 |

#### Electrical Characteristics (continued)

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2.5 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C, unless otherwise noted. All typical values are at  $T_A$  = 25°C.

|                 | PARAMETER                      | TEST CONDITIONS                                                  | MIN         | TYP  | MAX        | UNIT |

|-----------------|--------------------------------|------------------------------------------------------------------|-------------|------|------------|------|

| AC ACC          | URACY <sup>(4)</sup>           |                                                                  | •           |      |            |      |

|                 |                                | f <sub>IN</sub> = 2 kHz                                          | 94.4        | 96   |            |      |

| SINAD           | Signal-to-noise + distortion   | f <sub>IN</sub> = 100 kHz                                        |             | 95   |            | dB   |

|                 |                                | f <sub>IN</sub> = 500 kHz                                        |             | 83.9 |            |      |

|                 |                                | f <sub>IN</sub> = 2 kHz                                          | 94.5        | 96   |            |      |

| SNR             | Signal-to-noise ratio          | f <sub>IN</sub> = 100 kHz                                        |             | 95.9 |            | dB   |

|                 |                                | f <sub>IN</sub> = 500 kHz                                        |             | 84   |            |      |

|                 |                                | f <sub>IN</sub> = 2 kHz                                          |             | -118 |            |      |

| THD             | Total harmonic distortion (5)  | f <sub>IN</sub> = 100 kHz                                        |             | -102 |            | dB   |

|                 |                                | f <sub>IN</sub> = 500 kHz                                        |             | -101 |            |      |

|                 |                                | f <sub>IN</sub> = 2 kHz                                          |             | 120  |            |      |

| SFDR            | Spurious-free dynamic range    | f <sub>IN</sub> = 100 kHz                                        |             | 108  |            | dB   |

|                 |                                | f <sub>IN</sub> = 500 kHz                                        |             | 106  |            |      |

| DIGITAL         | . INPUTS (6)                   |                                                                  |             |      |            |      |

| V <sub>IH</sub> | High-level input voltage       |                                                                  | 0.65 DVDD   |      | DVDD + 0.3 | V    |

| V <sub>IL</sub> | Low-level input voltage        |                                                                  | -0.3        |      | 0.35 DVDD  | V    |

| DIGITAL         | OUTPUTS (6)                    |                                                                  | •           |      | •          |      |

| VoH             | High-level output voltage      | I <sub>OH</sub> = 2-mA source                                    | DVDD - 0.45 |      |            | ٧    |

| V <sub>OL</sub> | Low-level output voltage       | I <sub>OH</sub> = 2-mA sink                                      |             |      | 0.45       | V    |

| <b>POWER</b>    | SUPPLY                         |                                                                  |             |      |            |      |

| AVDD            | Analog supply voltage          |                                                                  | 1.65        | 1.8  | 1.95       | V    |

| DVDD            | Digital supply voltage         |                                                                  | 1.65        | 1.8  | 1.95       | V    |

|                 |                                | Active, 2.5-MSPS throughput,<br>T <sub>A</sub> = -40°C to +85°C  |             | 5    | 6.5        | 4    |

| IDD             | AVDD supply current            | Active, 2.5-MSPS throughput,<br>T <sub>A</sub> = -40°C to +125°C |             | 5    | 6.75       | mA   |

| 100             | (AVDD = 1.8 V)                 | Static, ACQ state                                                |             | 3.7  |            | mA   |

|                 |                                | Low-power, NAP mode                                              |             | 500  |            |      |

|                 |                                | Power-down, PD state                                             |             | 1    |            | μA   |

|                 |                                | Active, 2.5-MSPS throughput,<br>T <sub>A</sub> = -40°C to +85°C  |             | 9    | 11.7       | 14/  |

| PD              | AVDD power dissipation         | Active, 2.5-MSPS throughput,<br>T <sub>A</sub> = -40°C to +125°C |             | 9    | 12.15      | mW   |

|                 | (AVDD = 1.8 V)                 | Static, ACQ state                                                |             | 6.6  |            | mW   |

|                 |                                | Low-power, NAP mode                                              |             | 900  |            | \^/  |

|                 |                                | Power-down, PD state                                             |             | 1.8  |            | μW   |

| TEMPER          | RATURE RANGE                   | -                                                                |             |      |            |      |

| T <sub>A</sub>  | Operating free-air temperature |                                                                  | -40         |      | 125        | °C   |

#### 6.6 Timing Requirements: Conversion Cycle

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2.5 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  =  $-40^{\circ}$ C to +85°C. All typical values are at  $T_A$  = 25°C. See Figure 1.

|                        |                                       | MIN | TYP | MAX | UNIT |

|------------------------|---------------------------------------|-----|-----|-----|------|

| TIMING REQU            | JIREMENTS                             |     |     |     |      |

| f <sub>cycle</sub>     | Sampling frequency                    |     |     | 2.5 | MHz  |

| t <sub>cycle</sub>     | ADC cycle time period                 | 400 |     |     | ns   |

| twh_CONVST             | Pulse duration: CONVST high           | 30  |     |     | ns   |

| t <sub>wl_CONVST</sub> | Pulse duration: CONVST low            | 30  |     |     | ns   |

| t <sub>acq</sub>       | Acquisition time                      | 100 |     |     | ns   |

| t <sub>qt_acq</sub>    | Quiet acquisition time <sup>(1)</sup> | 25  |     |     | ns   |

| t <sub>d_cnvcap</sub>  | Quiet aperture time <sup>(1)</sup>    | 10  |     |     | ns   |

| TIMING SPEC            | CIFICATIONS                           |     |     |     |      |

| t <sub>conv</sub>      | Conversion time                       | 270 |     | 290 | ns   |

(1) See Figure 47.

#### 6.7 Timing Requirements: Asynchronous Reset, NAP, and PD

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2.5 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C. All typical values are at  $T_A$  = 25°C. See Figure 2 and Figure 3.

|                       |                                      | MIN | TYP | MAX  | UNIT |

|-----------------------|--------------------------------------|-----|-----|------|------|

| TIMING REQUI          | REMENTS                              |     |     |      |      |

| t <sub>wl_RST</sub>   | Pulse duration: RST low              | 100 |     |      | ns   |

| TIMING SPECI          | FICATIONS                            |     |     |      |      |

| t <sub>d_rst</sub>    | Delay time: RST rising to RVS rising |     |     | 1250 | μs   |

| t <sub>nap_wkup</sub> | Wake-up time: NAP mode               |     |     | 300  | ns   |

| t <sub>PWRUP</sub>    | Power-up time: PD mode               |     |     | 250  | μs   |

#### 6.8 Timing Requirements: SPI-Compatible Serial Interface

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF} = 5 V$ , and  $f_{DATA} = 2.5$  MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A = -40^{\circ}C$  to +85°C. All typical values are at  $T_A = 25^{\circ}C$ . See Figure 4.

|                        |                                       |                             | MIN   | TYP MAX | UNIT             |

|------------------------|---------------------------------------|-----------------------------|-------|---------|------------------|

| TIMING RE              | QUIREMENTS                            |                             |       |         | •                |

| f <sub>CLK</sub>       | Serial clock frequency                |                             |       | 75      | MHz              |

| t <sub>CLK</sub>       | Serial clock time period              |                             | 13.33 |         | ns               |

| t <sub>ph_CK</sub>     | SCLK high time                        |                             | 0.45  | 0.55    | t <sub>CLK</sub> |

| t <sub>pl_CK</sub>     | SCLK low time                         |                             | 0.45  | 0.55    | t <sub>CLK</sub> |

| t <sub>su_CSCK</sub>   | Setup time: CS falling to the first S | CLK capture edge            | 5     |         | ns               |

| t <sub>su CKDI</sub>   | Setup time: SDI data valid to the S   | CLK capture edge            | 1.2   |         | ns               |

| t <sub>ht_CKDI</sub>   | Hold time: SCLK capture edge to (     | previous) data valid on SDI | 0.65  |         | ns               |

| t <sub>ht_CKCS</sub>   | Delay time: last SCLK falling to CS   | rising                      | 5     |         | ns               |

| TIMING SPI             | ECIFICATIONS                          |                             |       |         |                  |

| t <sub>den_CSDO</sub>  | Delay time: CS falling to data enab   | le                          |       | 4.5     | i ns             |

| t <sub>dz CSDO</sub>   | Delay time: CS rising to SDO going    | g to 3-state                |       | 10      | ) ns             |

| t <sub>d_CKDO</sub>    | Delay time: SCLK launch edge to       | next) data valid on SDO     |       | 6.5     | i ns             |

| t <sub>d_CSRDY_f</sub> | Delay time: CS falling to RVS falling | g                           |       |         | i ns             |

|                        | Delay time:                           | After NOP operation         |       | 10      |                  |

| t <sub>d_CSRDY_r</sub> | CS rising to RVS rising               | After WR or RD operation    |       | 70      | ns               |

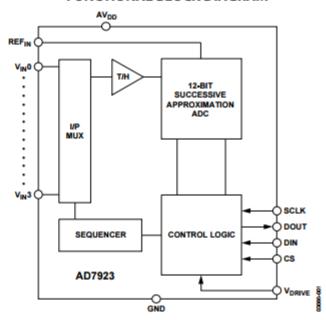

# 4-Channel, 200 kSPS 12-Bit ADC with Sequencer in 16-Lead TSSOP

**Data Sheet**

\$2.58 in 1000's

**AD7923**

#### **FEATURES**

Fast throughput rate: 200 kSPS Specified for AV<sub>DD</sub> of 2.7 V to 5.25 V

Low power

3.6 mW max at 200 kSPS with 3 V supply

7.5 mW max at 200 kSPS with 5 V supply

4 (single-ended) inputs with sequencer

Wide input bandwidth

70 dB Min SNR at 50 kHz input frequency

Flexible power/serial clock speed management

No pipeline delays

High speed serial interface SPI°-/QSPI™-/

MICROWIRE™-/DSP-compatible

Shutdown mode: 0.5 µA max

16-lead TSSOP package

Qualified for automotive applications

#### GENERAL DESCRIPTION

The AD7923 is a 12-bit, high speed, low power, 4-channel, suc-

#### FUNCTIONAL BLOCK DIAGRAM

#### **SPECIFICATIONS**

$AV_{DD} = V_{DRIVE} = 2.7 \text{ V}$  to 5.25 V,  $REF_{IN} = 2.5 \text{ V}$ ,  $f_{SCLK} = 20 \text{ MHz}$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 1.

| Table 1.                                            | nu : 1                     |            | T . C 1111 1C .                                                                   |

|-----------------------------------------------------|----------------------------|------------|-----------------------------------------------------------------------------------|

| Parameter                                           | B Version <sup>1</sup>     | Unit       | Test Conditions/Comments                                                          |

| DYNAMIC PERFORMANCE                                 |                            |            | $f_{IN} = 50 \text{ kHz}$ sine wave, $f_{SCLK} = 20 \text{ MHz}$                  |

| Signal-to-(Noise + Distortion) (SINAD) <sup>2</sup> | 70                         | dB min     | @ 5 V, =40°C to +85°C                                                             |

|                                                     | 69                         | dB min     | @ 5 V, 85℃ to 125℃, typ 70 dB                                                     |

|                                                     | 69                         | dB min     | @ 3 V typ 70 dB, =40°C to +125°C                                                  |

| Signal-to-Noise (SNR) <sup>2</sup>                  | 70                         | dB min     |                                                                                   |

| Total Harmonic Distortion (THD) <sup>2</sup>        | -77                        | dB max     | @ 5 V typ, -84 dB                                                                 |

|                                                     | -73                        | dB max     | @ 3 V typ,-77 dB                                                                  |

| Peak Harmonic or Spurious Noise                     | -78                        | dB max     | @ 5 V typ, -86 dB                                                                 |

| (SFDR) <sup>2</sup>                                 | -76                        | dB max     | @ 3 V typ, -80 dB                                                                 |

| Intermodulation Distortion (IMD) <sup>2</sup>       |                            |            | f <sub>A</sub> = 40.1 kHz, f <sub>B</sub> = 41.5 kHz                              |

| Second Order Terms                                  | -90                        | dB typ     |                                                                                   |

| Third Order Terms                                   | -90                        | dB typ     |                                                                                   |

| Aperture Delay                                      | 10                         | ns typ     |                                                                                   |

| Aperture Jitter                                     | 50                         | ps typ     |                                                                                   |

| Channel-to-Channel Isolation                        | -85                        | dB typ     | f <sub>IN</sub> = 400 kHz                                                         |

| Full Power Bandwidth                                | 8.2                        | MHz typ    | @ 3 dB                                                                            |

|                                                     | 1.6                        | MHz typ    | @ 0.1 dB                                                                          |

| DC ACCURACY <sup>2</sup>                            |                            |            | 0 511 52                                                                          |

| Resolution                                          | 12                         | Rits       |                                                                                   |

| Integral Nonlinearity                               | ±1                         | LSB max    |                                                                                   |

| Differential Nonlinearity                           | -0.9/+1.5                  | LSB max    | Guaranteed no missed codes to 12 bits                                             |

| 0 V to REF <sub>IN</sub> Input Range                | -0.9/+1.3                  | LSB IIIax  | Straight binary output coding                                                     |

| Offset Frror                                        | ±8                         | LSB max    | Typ ±0.5 LSB                                                                      |

| Offset Error Match                                  | ±0.5                       | LSB max    | 1yp ±0.3 £36                                                                      |

| Gain Error                                          | ±1.5                       | LSB max    |                                                                                   |

| Gain Error Match                                    | ±0.5                       | LSB max    |                                                                                   |

|                                                     | ±0.5                       | LSB max    | -REF <sub>IN</sub> to +REF <sub>IN</sub> biased about REF <sub>IN</sub> with twos |

| 0 V to 2 × REF <sub>IN</sub> Input Range            |                            |            | complement output coding                                                          |

| Positive Gain Error                                 | ±1.5                       | LSB max    |                                                                                   |

| Positive Gain Error Match                           | ±0.5                       | LSB max    |                                                                                   |

| Zero-Code Error                                     | ±8                         | LSB max    | Typ ±0.8 LSB                                                                      |

| Zero-Code Error Match                               | ±0.5                       | LSB max    | 1,7,2 = 1.0 = 2.2                                                                 |

| Negative Gain Error                                 | ±1                         | LSB max    |                                                                                   |

| Negative Gain Error Match                           | ±0.5                       | LSB max    |                                                                                   |

| ANALOG INPUT                                        | 10.5                       | LJD III dx |                                                                                   |

| Input Voltage Range                                 | 0 to REF <sub>IN</sub>     | v          | Range bit set to 1                                                                |

| input voltage hange                                 | 0 to 2 × REF <sub>IN</sub> | v          | Range bit set to 0, $AV_{DD} = 4.75 \text{ V to } 5.25 \text{ V}$                 |

| DC Leakage Current                                  | ±1                         | μA max     | hange bit set to 0, AVDD = 4.75 V to 5.25 V                                       |

| Input Capacitance                                   | 20                         |            |                                                                                   |

| REFERENCE INPUT                                     | 20                         | pF typ     |                                                                                   |

|                                                     | 2.5                        | v          | 140/                                                                              |

| REF <sub>IN</sub> Input Voltage                     | 2.5                        | 1 *        | ±1% specified performance                                                         |

| DC Leakage Current                                  | ±1                         | μA max     | , 2001 CDC                                                                        |

| REF <sub>IN</sub> Input Impedance                   | 36                         | kΩ typ     | f <sub>SAMPLE</sub> = 200 kSPS                                                    |

| LOGIC INPUTS                                        |                            |            |                                                                                   |

| Input High Voltage, VNH                             | 0.7 × VDRIVE               | V min      |                                                                                   |

| Input Low Voltage, VINL                             | 0.3 × VDRIVE               | V max      |                                                                                   |

| Input Current, I <sub>IN</sub>                      | ±1                         | μA max     | Typ 10 nA, V <sub>IN</sub> = 0 V or V <sub>DRIVE</sub>                            |

| Innut Canacitance C <sub>m</sub> <sup>3</sup>       | 10                         | nF may     | I                                                                                 |

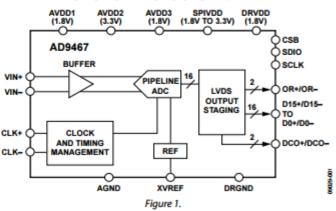

### 16-Bit, 200 MSPS/250 MSPS Analog-to-Digital Converter

Data Sheet \$120 in 1000's AD9467

#### **FEATURES**

75.5 dBFS SNR to 210 MHz at 250 MSPS 90 dBFS SFDR to 300 MHz at 250 MSPS SFDR at 170 MHz at 250 MSPS 92 dBFS at -1 dBFS 100 dBFS at -2 dBFS 60 fs rms jitter Excellent linearity at 250 MSPS  $DNL = \pm 0.5 LSB typical$ INL = ±3.5 LSB typical 2 V p-p to 2.5 V p-p (default) differential full-scale input (programmable) Integrated input buffer External reference support option Clock duty cycle stabilizer Output clock available Serial port control Built-in selectable digital test pattern generation Selectable output data format LVDS outputs (ANSI-644 compatible) 1.8 V and 3.3 V supply operation

#### APPLICATIONS

Multicarrier, multimode cellular receivers

Antenna array positioning

Power amplifier linearization

Broadband wireless

Radar

Infrared imaging

Communications instrumentation

#### FUNCTIONAL BLOCK DIAGRAM

A data clock output (DCO) for capturing data on the output is provided for signaling a new output bit.

The internal power-down feature supported via the SPI typically consumes less than 5 mW when disabled.

Optional features allow users to implement various selectable operating conditions, including input range, data format select, and output data test patterns.

The AD9467 is available in a Pb-free, 72-lead, LFCSP specified over the -40°C to +85°C industrial temperature range.

#### **SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.3 V, AVDD3 = 1.8 V, DRVDD = 1.8 V, specified maximum sampling rate, 2.5 V p-p differential input, 1.25 V internal reference, AIN = -1.0 dBFS, DCS on, default SPI settings, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                                           | Temp | Min  | Тур      | Max  | Unit    |

|------------------------------------------------------------------|------|------|----------|------|---------|

| RESOLUTION                                                       |      | 16   |          |      | Bits    |

| ACCURACY                                                         |      |      |          |      |         |

| No Missing Codes                                                 | Full |      | Guarante | ed   |         |

| Offset Error                                                     | Full | -200 | 0        | +200 | LSB     |

| Gain Error                                                       | Full | -3.9 | -0.1     | +2.6 | %FSR    |

| Differential Nonlinearity (DNL) <sup>2</sup>                     | Full | -0.9 | ±0.5     | +1.5 | LSB     |

| Integral Nonlinearity (INL) <sup>2</sup>                         | Full | -12  | ±3.5     | +12  | LSB     |

| TEMPERATURE DRIFT                                                |      |      |          |      |         |

| Offset Error                                                     | Full |      | ±0.023   |      | %FSR/°C |

| Gain Error                                                       | Full |      | ±0.036   |      | %FSR/°C |

| ANALOG INPUTS                                                    |      |      |          |      |         |

| Differential Input Voltage Range (Internal VREF = 1 V to 1.25 V) | Full | 2    | 2.5      | 2.5  | V p-p   |

| Common-Mode Voltage                                              | 25°C |      | 2.15     |      | V       |

| Differential Input Resistance                                    | 25°C |      | 530      |      | Ω       |

| Differential Input Capacitance                                   | 25°C |      | 3.5      |      | pF      |

| Full Power Bandwidth                                             | 25°C |      | 900      |      | MHz     |

| XVREF INPUT                                                      |      |      |          |      |         |

| Input Voltage                                                    | Full | 1    |          | 1.25 | V       |

| Input Capacitance                                                | Full |      | 3        |      | pF      |

| POWER SUPPLY                                                     |      |      |          |      |         |

| AVDD1                                                            | Full | 1.75 | 1.8      | 1.85 | V       |

| AVDD2                                                            | Full | 3.0  | 3.3      | 3.6  | V       |

| AVDD3                                                            | Full | 1.7  | 1.8      | 1.9  | V       |

| DRVDD                                                            | Full | 1.7  | 1.8      | 1.9  | V       |

| I <sub>AVDD1</sub>                                               | Full |      | 567      | 620  | mA      |

| I <sub>AVDD2</sub>                                               | Full |      | 55       | 61   | mA      |

| l <sub>AVDD3</sub>                                               | Full |      | 31       | 35   | mA      |

| I <sub>DRVDD</sub>                                               | Full |      | 40       | 43   | mA      |

| Total Power Dissipation (Including Output Drivers)               | Full |      | 1.33     | 1.5  | W       |

| Power-Down Dissipation                                           | Full |      | 4.4      | 90   | mW      |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed.

<sup>&</sup>lt;sup>2</sup> Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

#### **AC SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.3 V, AVDD3 = 1.8 V, DRVDD = 1.8 V, specified maximum sampling rate, 2.5 V p-p differential input, 1.25 V internal reference, AIN = -1.0 dBFS, DCS on, default SPI settings, unless otherwise noted.

Table 2.

| Table 2.                                                                            |      |      |           |     |       |

|-------------------------------------------------------------------------------------|------|------|-----------|-----|-------|

| Parameter <sup>1</sup>                                                              | Temp | Min  | Тур       | Max | Unit  |

| ANALOG INPUT FULL SCALE                                                             |      | 2.5  | 2/2.5     |     | V p-p |

| SIGNAL-TO-NOISE RATIO (SNR)                                                         |      |      |           |     |       |

| $f_N = 5 \text{ MHz}$                                                               | 25°C |      | 74.7/76.4 |     | dBFS  |

| $f_N = 97 \text{ MHz}$                                                              | 25°C |      | 74.5/76.1 |     | dBFS  |

| f <sub>IN</sub> = 140 MHz                                                           | 25°C |      | 74.4/76.0 |     | dBFS  |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 73.7 | 74.3/75.8 |     | dBFS  |

|                                                                                     | Full | 71.5 |           |     | dBFS  |

| f <sub>IN</sub> = 210 MHz                                                           | 25°C |      | 74.0/75.5 |     | dBFS  |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 73.3/74.6 |     | dBFS  |

| SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD)                                        |      |      |           |     |       |

| f <sub>N</sub> = 5 MHz                                                              | 25°C |      | 74.6/76.3 |     | dBFS  |

| $f_N = 97 \text{ MHz}$                                                              | 25°C |      | 74.4/76.0 |     | dBFS  |

| f <sub>N</sub> = 140 MHz                                                            | 25°C |      | 74.4/76.0 |     | dBFS  |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 72.4 | 74.2/75.8 |     | dBFS  |

|                                                                                     | Full | 71.0 |           |     | dBFS  |

| f <sub>N</sub> = 210 MHz                                                            | 25°C |      | 73.9/75.4 |     | dBFS  |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 73.1/74.4 |     | dBFS  |

| EFFECTIVE NUMBER OF BITS (ENOB)                                                     |      |      |           |     |       |

| fn = 5 MHz                                                                          | 25°C |      | 12.1/12.4 |     | Bits  |

| f <sub>N</sub> = 97 MHz                                                             | 25°C |      | 12.1/12.3 |     | Bits  |

| f <sub>N</sub> = 140 MHz                                                            | 25°C |      | 12.1/12.3 |     | Bits  |

| f <sub>IN</sub> = 170 MHz                                                           | 25°C |      | 12.0/12.3 |     | Bits  |

| ig = 170 mile                                                                       | Full | 11.5 | 12.0/12.3 |     | Bits  |

| $f_{IN} = 210 \text{ MHz}$                                                          | 25°C |      | 12.0/12.2 |     | Bits  |

| f <sub>IN</sub> = 300 MHz                                                           | 25°C |      | 11.9/12.1 |     | Bits  |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR) (INCLUDING SECOND AND THIRD HARMONIC DISTORTION) |      |      | ,         |     |       |

| fix = 5 MHz                                                                         | 25°C |      | 98/97     |     | dBES  |

| f <sub>N</sub> = 97 MHz                                                             | 25°C |      | 95/93     |     | dBFS  |

| f <sub>IN</sub> = 140 MHz                                                           | 25°C |      | 94/95     |     | dBFS  |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 82   | 93/92     |     | dBFS  |

| IN = 170 MILE                                                                       | Full | 82   | 33/32     |     | dBF9  |

| f <sub>IN</sub> = 210 MHz                                                           | 25°C | 02   | 93/92     |     | dBFS  |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 93/90     |     | dBFS  |

| SFDR (INCLUDING SECOND AND THIRD HARMONIC DISTORTION)                               | 250  |      | 33/30     |     | ubi . |

| fix = 5 MHz at -2 dB Full Scale                                                     | 25°C |      | 100/100   |     | dBFS  |

| f <sub>N</sub> =97 MHz at =2 dB Full Scale                                          | 25°C |      | 97/97     |     | dBFS  |

| fin = 140 MHz at = 2 dB Full Scale                                                  | 25°C |      | 100/95    |     | dBFS  |

| f <sub>N</sub> = 170 MHz at -2 dB Full Scale                                        | 25°C |      | 100/93    |     | dBFS  |

| f <sub>N</sub> = 210 MHz at -2 dB Full Scale                                        | 25°C |      | 93/93     |     | dBFS  |

| f <sub>N</sub> = 300 MHz at -2 dB Full Scale                                        | 25°C |      | 90/90     |     | dBFS  |

|                                                                                     | 25 C |      | 90/90     |     | ubr.  |

| WORST OTHER (EXCLUDING SECOND AND THIRD HARMONIC DISTORTION)  fin = 5 MHz           | 2596 |      | 00/07     |     | -IDE  |

| $t_N = 5 \text{ MHz}$ $t_N = 97 \text{ MHz}$                                        | 25°C |      | 98/97     |     | dBF9  |

|                                                                                     |      |      | 97/93     |     | dBF5  |

| f <sub>N</sub> = 140 MHz                                                            | 25°C |      | 97/95     |     | dBFS  |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 88   | 97/93     |     | dBFS  |

| (                                                                                   | Full | 82   |           |     | dBFS  |

| f <sub>N</sub> = 210 MHz                                                            | 25°C |      | 97/95     |     | dBFS  |

| $f_{IN} = 300 \text{ MHz}$                                                          | 25°C | 1    | 97/95     |     | dBFS  |

#### SWITCHING SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.3 V, AVDD3 = 1.8 V, DRVDD = 1.8 V, specified maximum sampling rate, 2.5 V p-p differential input, 1.25 V internal reference, AIN = -1.0 dBFS, DCS on, default SPI settings, unless otherwise noted.

Table 4.

| Parameter <sup>1</sup>                   | Temp | Min  | Тур | Max  | Unit         |

|------------------------------------------|------|------|-----|------|--------------|

| CLOCK <sup>2</sup>                       |      |      |     |      |              |

| Clock Rate                               | Full | 50   |     | 250  | MSPS         |

| Clock Pulse Width High (tc+)             | Full |      | 2   |      | ns           |

| Clock Pulse Width Low (ta)               | Full |      | 2   |      | ns           |

| OUTPUT PARAMETERS <sup>2, 3</sup>        |      |      |     |      |              |

| Propagation Delay (tpp)                  | 25°C |      | 3   |      | ns           |

| Rise Time (t <sub>R</sub> ) (20% to 80%) | 25°C |      | 200 |      | ps           |

| Fall Time (t <sub>F</sub> ) (20% to 80%) | 25°C |      | 200 |      | ps           |

| DCO Propagation Delay (tcro)             | 25°C |      | 3   |      | ns           |

| DCO to Data Delay (t <sub>sxew</sub> )   | Full | -200 |     | +200 | ps           |

| Wake-Up Time (Power-Down)                | Full |      | 100 |      | ms           |

| Pipeline Latency                         | Full |      | 16  |      | Clock cycles |

| APERTURE                                 |      |      |     |      |              |

| Aperture Delay (t <sub>A</sub> )         | 25°C |      | 1.2 |      | ns           |

| Aperture Uncertainty (Jitter)            | 25°C |      | 60  |      | fs rms       |

| Out-of-Range Recovery Time               | 25°C |      | 1   |      | Clock cycles |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed.

<sup>&</sup>lt;sup>2</sup> Can be adjusted via the SPI interface.

Managements were made using a part coldered to ED.4 material

Designers must understand performance requirements!

Users must be aware of the "quirks" inherent in data converters!

### Performance Characterization of Data Converters

### Static characteristics

- Resolution

- Least Significant Bit (LSB)

- Offset and Gain Errors

- Absolute Accuracy

- Relative Accuracy

- Integral Nonlinearity (INL)

- Differential Nonlinearity (DNL)

- Monotonicity (DAC)

- Missing Codes (ADC)

- Low-f Spurious Free Dynamic Range (SFDR)

- Low-f Total Harmonic Distortion (THD)

- Effective Number of Bits (ENOB)

- Power Dissipation

#### Performance Characterization of Data Converters

- Dynamic characteristics

- Conversion Time or Conversion Rate (ADC)

- Settling time or Clock Rate (DAC)

- Sampling Time Uncertainty (aperture uncertainty or aperture jitter)

- Dynamic Range

- Spurious Free Dynamic Range (SFDR)

- Total Harmonic Distortion (THD)

- Signal to Noise Ratio (SNR)

- Signal to Noise and Distortion Ratio (SNDR)

- Sparkle Characteristics

- Effective Number of Bits (ENOB)

# Dynamic characteristics

- Degradation of dynamic performance parameters often due to nonideal effects in time-domain performance

- Dynamic characteristics of high resolution data converters often challenging to measure, to simulate, to understand source of contributions, and to minimize

Example: An n-bit ADC would often require SFDR at the 6n+6 bit level or better. Thus, considering a 14-bit ADC, the SFDR would be expected to be at the -90dB level or better. If the input to the ADC is a 1V p-p sinusoidal waveform, the second harmonic term would need to be at the  $10^{(-90dB/20dB)} = 32\mu\text{V}$  level. A 32uV level is about 1part in 30,000. Signals at this level are difficult to accurately simulate in the presence of a 1V level signal. For example, convergence parameters in simulators and sample (strobe) points used in data acquisition adversely affect simulation results and observing the time domain waveforms that contribute to nonlinearity at this level and relationships between these waveforms and the sources of nonlinearity is often difficult to visualize. Simulation errors that are at the 20dB level or worse can occur if the simulation environment is not correctly established.

#### Performance Characterization of Data Converters

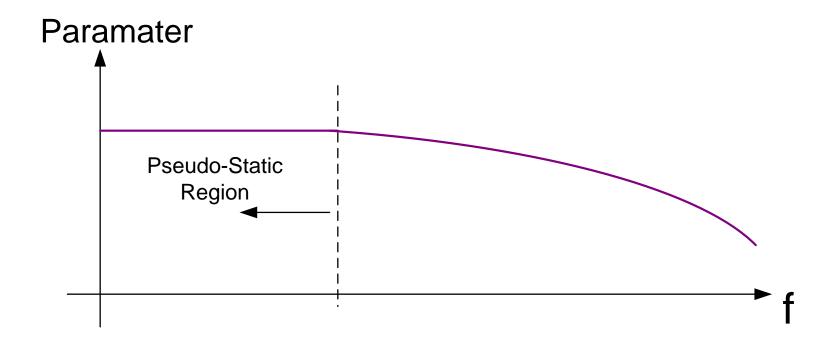

What is meant by "low frequency"?

Operation at frequencies so low that further decreases in frequency cause no further changes in a parameter of interest

Low frequency operation is often termed Pseudostatic operation

# Low-frequency or Pseudo-Static Performance

#### Performance Characterization of Data Converters

#### Static characteristics

- Resolution

- Offset and Gain Errors

- Absolute Accuracy

- Relative Accuracy

- - Differential Nonlinearity (DNL)

- Monotonicity (DAC)

- Missing Codes (ADC)

- Low-f Spurious Free Dynamic Range (SFDR)

- Low-f Total Harmonic Distortion (THD)

- Effective Number of Bits (ENOB)

- Power Dissipation

#### Resolution

- Number of distinct analog levels in a DAC

- Number of digital output codes in ADC

- In most cases this is a power of 2

- If a converter can resolve 2<sup>n</sup> levels, then we term it an n-bit converter

- 2<sup>n</sup> analog outputs for an n-bit DAC

- 2<sup>n</sup>-1 transition points for an n-bit ADC

- Resolution is often determined by architecture and thus not measured

- Effective resolution can be defined and measured

- If N<sub>x</sub> levels can be resolved for an DAC then

$$n_{EQ} = \frac{\log N_x}{\log 2}$$

If N<sub>x</sub>-1 transition points in an ADC, then

$$n_{EQ} = \frac{\log N_x}{\log 2}$$

#### **Least Significant Bit**

Assume

$$N = 2^{n}$$

# Generally <u>Defined</u> by Manufacturer to be $\mathcal{X}_{\text{LSB}} = \mathcal{X}_{\text{REF}} / \mathbb{N}$

#### Effective Value of LSB can be Measured

For DAC:  $\mathcal{X}_{LSB}$  is equal to the <u>maximum</u> increment in the output for a single bit change in the Boolean input

For ADC:  $\mathcal{X}_{LSB}$  is equal to the <u>maximum</u> distance between two adjacent transition points

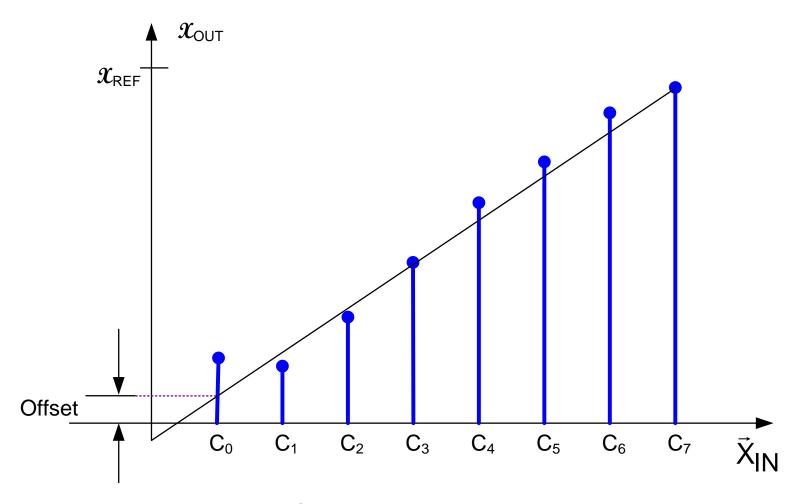

**Offset**

For DAC the offset is (assuming 0 is ideal value of  $\mathcal{X}_{\text{OUT}}(<0,...0>)$

$$\mathcal{X}_{\text{OUT}}$$

(<0,...,0>) - absolute  $\underline{\mathcal{X}_{\text{OUT}}}$  - in LSB - in LSB

(If ideal value of  $\mathcal{X}_{OUT}(<0,...0>) \neq 0$ , offset is shift from ideal value at <0,...0>)

#### Offset (for DAC)

- Offset strongly (totally) dependent upon performance at a single point

- Probably more useful to define relative to a fit of the data

# Offset (for DAC)

Offset relative to fit of data

#### **Offset**

For ADC the offset is (assuming  $\mathcal{X}_{LSB}$  is the ideal first transition point)

$$\begin{array}{c} \mathcal{X}_{\text{T1}} - \mathcal{X}_{\text{LSB}} \\ \hline \mathcal{X}_{\text{LSB}} \\ \hline \mathcal{X}_{\text{LSB}} \\ \hline \\ \mathcal{X}_{\text{LSB}} \\ \hline \\ \mathcal{X}_{\text{LSB}} \\ \hline \\ \mathcal{X}_{\text{OUT}} \\ \hline \\ \mathcal{X}_{\text{OFFSET}} \\ \hline \\ \mathcal{X}_{\text{REF}} \\ \hline \\ - \text{ absolute}$$

(If ideal first transition point is not  $\mathcal{X}_{LSB}$ , offset is shift from ideal)

#### Offset

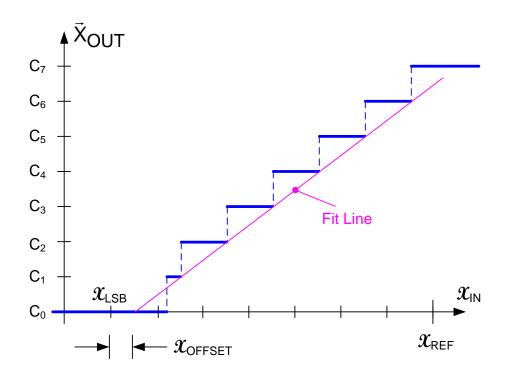

For ADC the offset is

- · Offset strongly (totally) dependent upon performance at a single point

- Probably more useful to define relative to a fit of the data

#### **Offset**

For ADC the offset is

Offset relative to fit of data

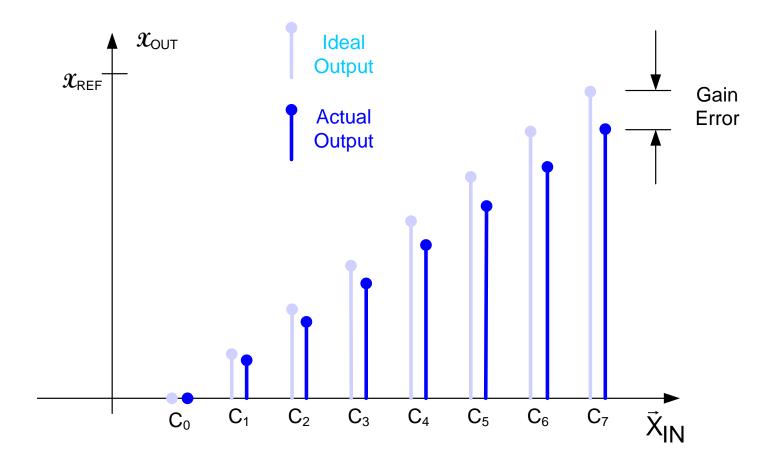

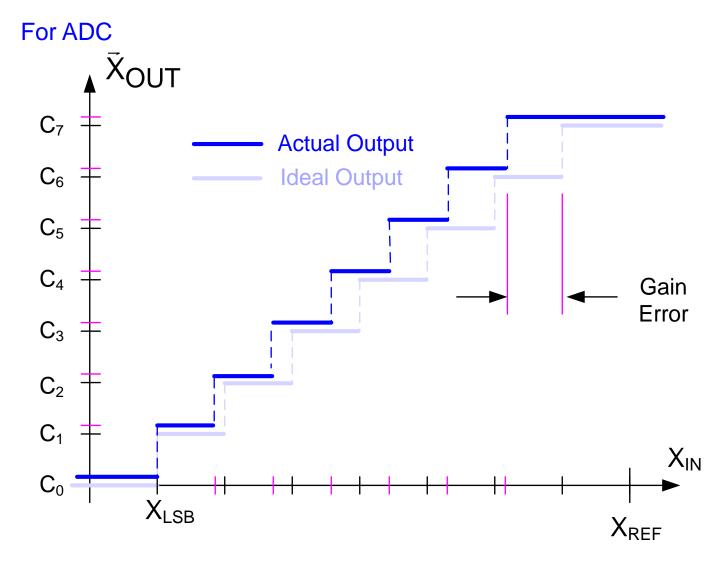

#### **Gain and Gain Error**

For DAC

Gain error determined after offset is subtracted from output

#### **Gain and Gain Error**

Gain error determined after offset is subtracted from output

#### **Gain and Offset Errors**

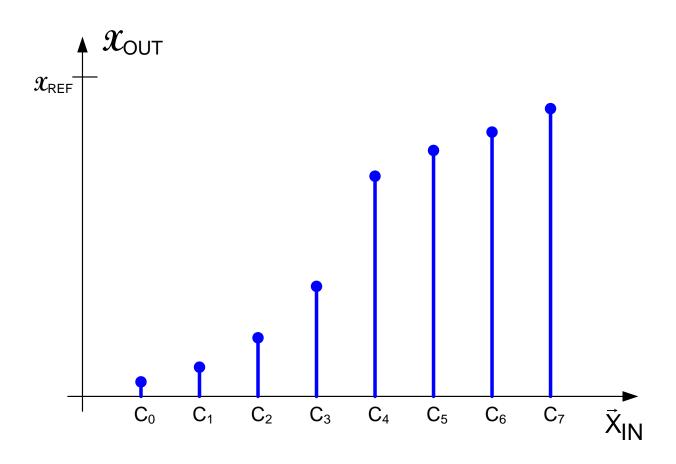

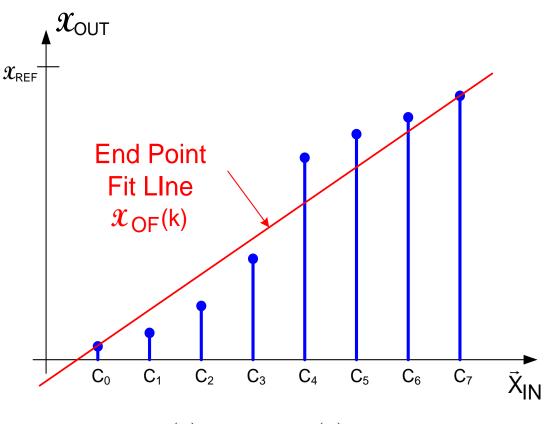

- Fit line would give better indicator of error in gain but less practical to obtain in test

- Gain and Offset errors of little concern in many applications

- Performance characteristic of interest often nearly independent of gain and offset errors

- Can be trimmed in field if gain or offset errors exist.

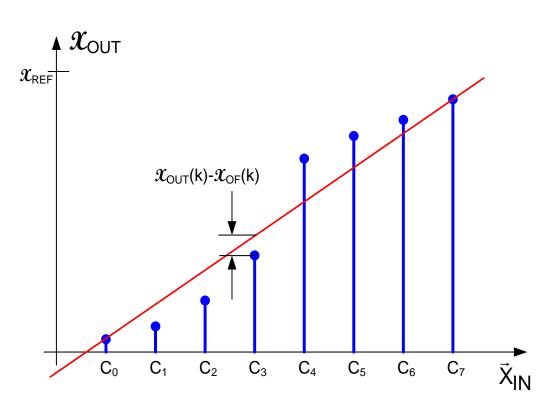

$$\mathcal{X}_{OF}(k) = mk + \mathcal{X}_{OUT}(0)$$

$$m = \frac{\mathcal{X}_{OUT}(N-1) - \mathcal{X}_{OUT}(0)}{N-1}$$

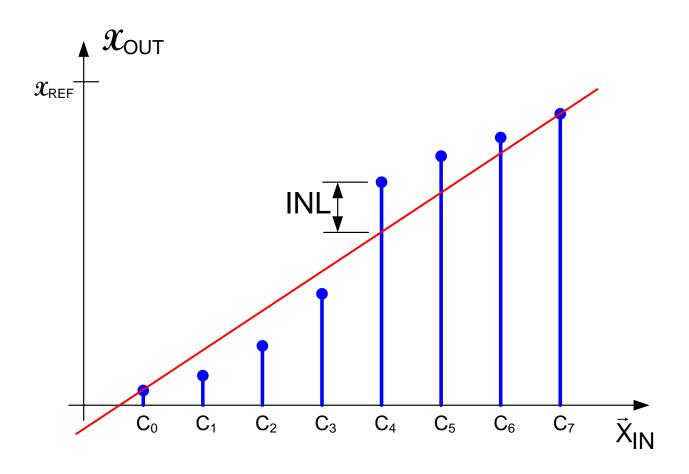

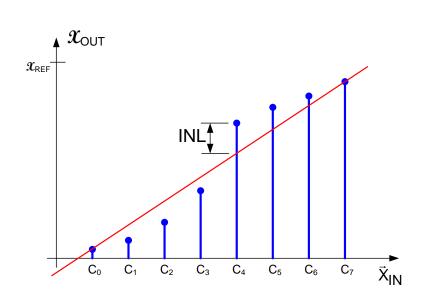

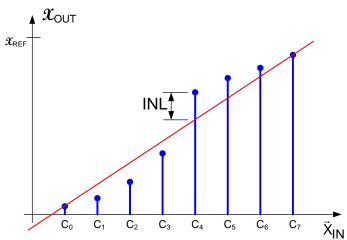

$$INL_{k} = \mathcal{X}_{OUT}(k) - \mathcal{X}_{OF}(k)$$

$$INL = \max_{0 \le k \le N-1} \{ |INL_k| \}$$

#### **Nonideal DAC**

INL often expressed in LSB

$$\mathsf{INL}_{\mathsf{k}} = \frac{\mathcal{X}_{\mathsf{OUT}}(\mathsf{k}) \text{-} \mathcal{X}_{\mathsf{OF}}(\mathsf{k})}{\mathcal{X}_{\mathsf{LSB}}}$$

$$INL = \max_{0 \le k \le N-1} \{ |INL_k| \}$$

- INL is often the most important parameter of a DAC

- INL<sub>0</sub> and INL<sub>N-1</sub> are 0 (by definition)

- There are N-2 elements in the set of INL<sub>k</sub> that are of concern

- INL is almost always nominally 0 (i.e. designers try to make it 0)

- INL is a random variable at the design stage

- INL<sub>k</sub> is a random variable for 0<k<N-1</li>

- $INL_k$  and  $INL_{k+j}$  are almost always correlated for all k,j (not incl 0, N-1)

- Fit Line is a random variable

- INL is the N-2 order statistic of a set of N-2 correlated random variables

- At design stage, INL characterized by standard deviation of the random variable

- Closed-form expressions for INL almost never exist because PDF of order statistics of correlated random variables is extremely complicated

- Simulation of INL very time consuming if n is very large (large sample size required to establish reasonable level of confidence)

- Model parameters become random variables

- Process parameters affect multiple model parameters causing model parameter correlation

- Simulation times can become very large

- INL can be readily measured in laboratory but often dominates test costs because of number of measurements needed when n is large

- Expected value of INL<sub>k</sub> at k=(N-1)/2 is largest for many architectures

- Major effort in DAC design is in obtaining acceptable INL yield!

Stay Safe and Stay Healthy!

# End of Lecture 25